Lattice GAL22V10D-25QJN: Architecture, Key Features, and Target Applications

The Lattice GAL22V10D-25QJN stands as a classic and highly influential device in the history of programmable logic. As a member of the Generic Array Logic (GAL) family, it provided a powerful, erasable, and electrically reprogrammable alternative to one-time programmable PAL devices, revolutionizing digital design prototyping and production. This article delves into its internal architecture, its defining characteristics, and the modern applications where it continues to offer value.

Architecture: A Look Inside

The architecture of the GAL22V10D is a sophisticated evolution of simple PLDs. Its core structure is based on a programmable AND array that feeds into a fixed OR array. This arrangement allows designers to create a wide range of sum-of-products logic functions.

The key architectural component is the Output Logic Macrocell (OLMC). The device features 10 of these macrocells, each associated with an output pin. The power of the GAL lies in the flexibility of these macrocells. Each OLMC can be individually configured by the user to operate in several modes:

Combinatorial Mode: The output is solely a function of the AND-OR array.

Registered Mode: The output is stored in a D-type flip-flop, synchronizing the output to a clock signal, which is essential for state machines and counters.

Complex Mode: Allows for more advanced configurations, such as using the feedback path from the output back into the AND array.

This reprogrammable macrocell architecture eliminated the need for multiple fixed-function PAL parts, making the GAL22V10D a true "universal" programmable logic device.

Key Features and Specifications

The "22V10" nomenclature succinctly summarizes its core capabilities: 22 inputs and 10 outputs. The specific part number, GAL22V10D-25QJN, reveals further critical details:

Technology: Based on CMOS EECMOS (Electrically Erasable CMOS) technology. This allowed the device to be reprogrammed thousands of times, drastically reducing development time and cost.

Speed: The suffix `-25` denotes a maximum propagation delay of 25 ns, making it suitable for clock frequencies up to 40 MHz in many applications.

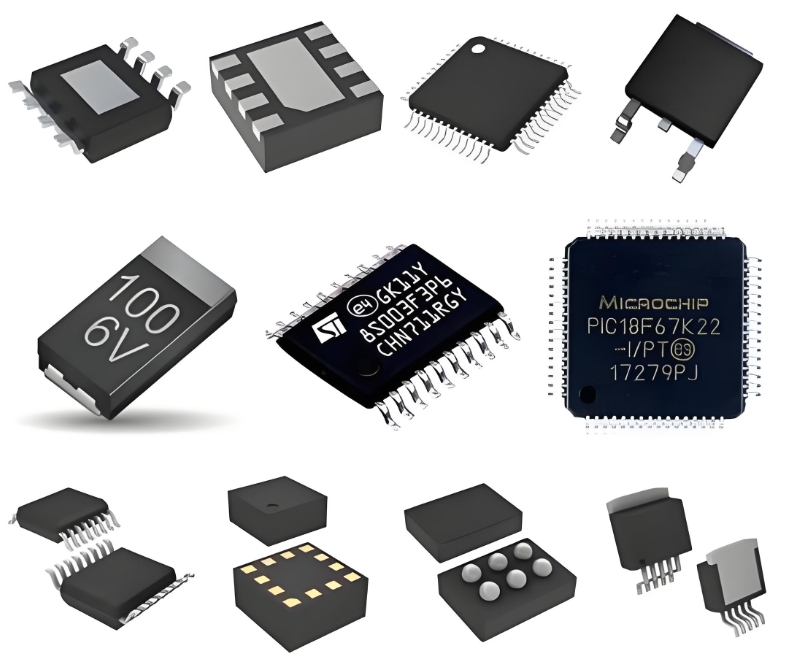

Package: The `QJN` indicates a 28-pin Plastic Leaded Chip Carrier (PLCC) package, a common surface-mount format for the era.

Low Power: The CMOS design ensures very low power consumption compared to its bipolar counterparts, a significant advantage for portable and power-sensitive systems.

Target Applications: Legacy and Modern Use

While surpassed in complexity by modern CPLDs and FPGAs, the GAL22V10D-25QJN remains relevant in several key areas:

Legacy System Maintenance and Repair: It is indispensable for supporting and repairing older industrial control, military, and communications equipment where original parts are obsolete.

Glue Logic Integration: Perfect for consolidating a large number of discrete logic ICs (e.g., 74-series) into a single, compact chip, reducing board space and improving reliability.

Educational Tool: Its simplicity makes it an excellent tool for teaching fundamental digital logic design, state machine implementation, and the principles of programmable logic.

Prototyping and Low-Volume Production: Its fast compile times and simple design flow allow for rapid iteration of simple logic designs without the overhead of a complex FPGA toolchain.

Interface Logic and State Machines: Continues to be effectively used for implementing address decoders, bus controllers, and simple finite state machines in embedded systems.

The Lattice GAL22V10D-25QJN is a foundational pillar of programmable logic. Its elegant and flexible macrocell-based architecture, electrically erasable technology, and proven reliability have secured its place as a timeless solution. For engineers working with legacy systems, designing simple control logic, or teaching the fundamentals of hardware design, it remains an incredibly valuable and effective component, demonstrating that powerful solutions often lie in elegant simplicity.

Keywords:

Programmable Logic Device (PLD)

Output Logic Macrocell (OLMC)

EECMOS Technology

Glue Logic

State Machine